### УДК 681.3.06

# НЕРЕКУРСИВНАЯ ФИЛЬТРАЦИЯ ИЗОБРАЖЕНИЙ С ИСПОЛЬЗОВАНИЕМ ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ АРХИТЕКТУРЫ FPGA

## В.М. ЧЕРТКОВ, канд. техн. наук, доц. Р.П. БОГУШ, А.В. АНДРОЩУК (Полоцкий государственный университет)

Представлена структура двумерного нерекурсивного фильтра с использованием ПЛИС архитектуры FPGA для обработки крупноформатных изображений. При этом применен параллельно-конвейерный алгоритм. Представлена модель устройства, которая разработана и исследована в программном продукте Simulink. Для аппаратной реализации предлагается использовать ПЛИС XC6SLX75 семейства Spartan-6. В среде разработки Xilinx ISE определена максимальная задержка в цепях внутренней структуры ПЛИС. Рассчитана скорость обработки для двумерных фильтров различных размеров и представлены примеры обработки.

Введение. Обеспечение высокой производительности обработки крупноформатных изображений является актуальной задачей. Развитие технологий цифровой обработки изображений и внедрение их в различные производственные области предполагает значительное увеличение вычислительных затрат. Это приводит к необходимости совершенствования алгоритмической базы и использованию высокопроизводительных систем обработки. Одним из подходов повышения производительности вычислений является распараллеливание процесса обработки [1], которое в большинстве случаев реализуется при помощи специализированных интегральных схем (ИС), таких как программируемые логические интегральные схемы (ПЛИС) типа Field Programmable Gate Array (FPGA) [2]. Интегральные схемы такого типа представляют программируемую логическую матрицу (ПЛМ), между элементами которой проложены электрически коммутируемые соединения. Это позволяет конфигурировать отдельные компоненты и создавать связи между ними путем загрузки в ПЛИС потока данных, включающего требуемые цепи и узлы коммутации. В результате из имеющихся в составе ПЛМ ресурсов создается требуемая цифровая схема, которая при необходимости может быть легко модифицирована. Современные ПЛИС имеют достаточно большой объем ресурсов, достигающий миллионов эквивалентных логических вентилей, составляющих сотни тысяч логических ячеек, что позволяет проектировать цифровые устройства практически любой сложности [3]. Самые распространенные ПЛИС Xilinx и Altera содержат в архитектуре своих устройств специализированные модули DSP, которые могут выполнять умножение с накоплением с максимальной производительностью и перспективны для высокоскоростной обработки изображений [4].

**Основная часть.** Одной из базовых операций при цифровой обработке изображений является операция вычисления свертки. Данная операция широко используется при цифровой фильтрации, идентификации характеристик и оценивании параметров систем, классификации и распознавании образов, прогнозировании и моделировании. Корреляционная обработка и пространственная фильтрация – разновидности сверточного преобразования, т.е. они являются связанными, что предполагает вычисление суммы произведений над входными данными.

В задачах обработки изображений используют двумерные фильтры. Нерекурсивный двумерный фильтр с конечной импульсной характеристикой реализует свертку, т.е. за значение пикселя выходного изображения G(n,m) принимается взвешенная сумма конечного числа пикселей обрабатываемого изображения F(n,m):

$$G(n,m) = \sum_{k} \sum_{l \in D} h(n,m) F(n-k,m-l) , \qquad (1)$$

где h(k,l) — двумерная матрица коэффициентов; h(k,l) — коэффициенты фильтра; D — опорная область (размер окна, апертура) фильтра.

В случае высоких динамических искажений апертура фильтра имеет значительные размеры, из-за чего существенно возрастают вычислительные затраты, которые для каждого положения окна фильтра на изображении определяются необходимым числом операций умножения  $(k \times l)$  и необходимым числом операций сложения вычитания  $(k \times (l-1))$ . При этом количество положений фильтра на изображении оценивается как  $(m-l+1)\times (n-k+1)$ . Уменьшение размеров опорной области фильтра при значительных динамических искажениях входного изображения ухудшают качество обработанного изображения [5].

Цель работы – повышение быстродействия процедуры нерекурсивной двумерной фильтрации изображений за счет разработки и применения параллельно-конвейерного алгоритма с использованием ПЛИС архитектуры FPGA.

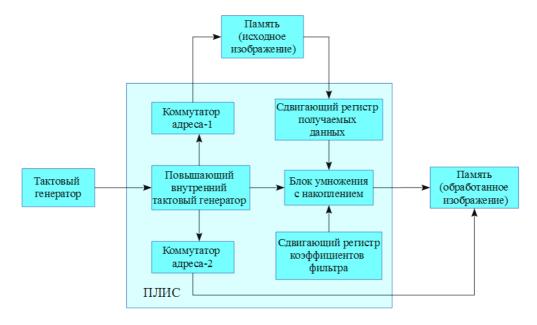

Методика эксперимента. Процедура фильтрации предполагает наложение окна фильтра на фрагмент изображения, вычисление результирующего значения для центрального элемента в пределах обрабатываемой области и последующий сдвиг окна на один пиксель вправо или вниз на один пиксель и влево на начало строки, т.е. окно скользит по изображению с верхнего левого края до правого нижнего. На основе данного подхода разработана внутренняя структура ПЛИС и алгоритм фильтрации полутоновых изображений с применением высокоскоростной памяти. Особенность подхода заключается в том, что из i-1 строки изображения считываются и заполняют входной сдвиговый регистр по n пикселей (для маски размером  $n \times n$ ), значения которых умножаются на соответствующие коэффициенты фильтра с последующим суммированием и записью результата в память. Особенностью разработанной структуры является возможность загрузки любого пикселя обрабатываемого изображения из высокоскоростной памяти во входной регистр, который состоит из сдвиговых регистров, соединенных определенным образом. Применяя данный метод можно сократить число запоминающих элементов до  $n \times n$  для хранения отдельных пикселей исходного изображения при окне фильтра  $n \times n$ , обеспечивая высокую скорость обработки данных. Структурная схема, реализующая представленный способ двумерной фильтрации изображения с применением высокоскоростной памяти для хранения исходного изображения и результата обработки на базе ПЛИС, представлена на рисунке 1. Схема включает: тактовый генератор, который обеспечивает стабильную входную частоту до 100 МГц; повышающий внутренний тактовый генератор; коммутатор адреса 1, позволяющий загружать из памяти отдельные пиксели по задаваемому адресу; память для хранения; сдвигающий регистр получаемых данных, предназначенный для сдвига и хранения пикселей входного изображения; сдвигающий регистр коэффициентов фильтра, который хранит коэффициенты фильтра и осуществляет циклический сдвиг; блок умножения с накоплением, выполняющий свертку загруженных данных с коэффициентами фильтра; коммутатор адреса 2, который определяет адрес ячейки памяти для записи результата фильтрации на этапе обработки.

Рисунок 1 – Структурная схема двумерной фильтрации изображений на ПЛИС

Цветное изображение описывается значениями интенсивности пикселя, как правило, для трех каналов системы цветности RGB. Таким образом, для фильтрации могут быть использованы три фильтра, построенные по рассмотренной схеме и работающие параллельно во времени, которые могут быть размещены в одной ПЛИС.

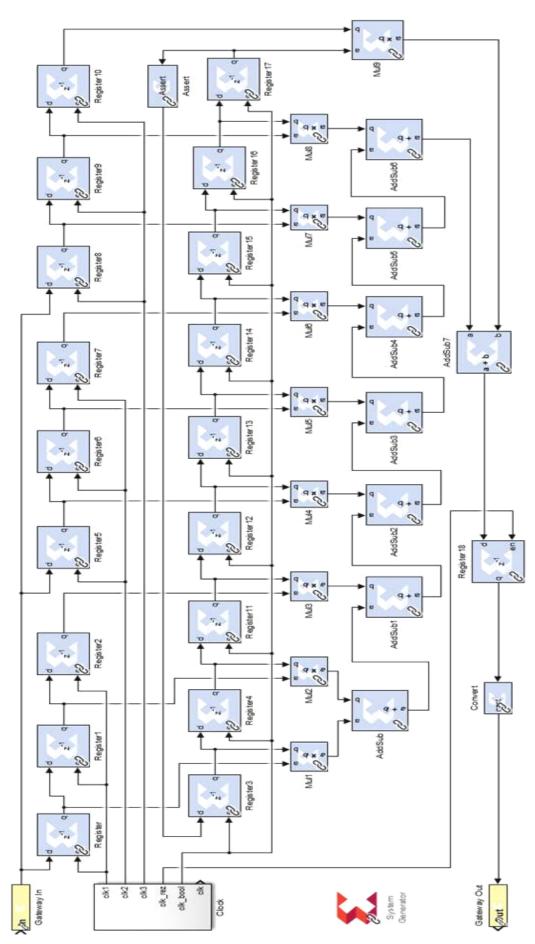

Разработанная структура реализована в среде моделирования Simulink и представлена на рисунке 2. С использованием данной структуры подготовлены исходные данные и результат моделирования фильтра.

С помощью программного обеспечения систем MATLAB, Xilinx system generator среды Xilinx ISE 14.7 [6] синтезирована модель на языке описания аппаратуры Verilog для ПЛИС семейства Spartran-6.

Рисунок 2 - Структурная модель двумерной фильтрации с апертурой размером 3×3

Основные характеристики выбранной ПЛИС приведены в таблице 1. Подбор ПЛИС осуществляется с учетом соответствия ее характеристик модели, синтезированой на языке описания аппаратуры Verilog.

Таблица 1 – Характеристики ПЛИС XC6SLX75 семейства Spartan-6

| Количество<br>секций Slices | Число логических ячеек Logic Cells | Аппаратные секции DSP48A1 | Доступные контакты<br>ввода/вывода | Максимальная системная<br>частота тактирования |  |

|-----------------------------|------------------------------------|---------------------------|------------------------------------|------------------------------------------------|--|

| 11 662                      | 74 637                             | 132                       | 400                                | 1000 МГЦ                                       |  |

В качестве примера использования ПЛИС для скоростной обработки полутоновых изображений и для определения времени на обработку одного пикселя используется изображение размером  $512 \times 512$  пикселей и двумерный сглаживающий фильтр вида

$$h = \begin{bmatrix} 1/16 & 1/8 & 1/16 \\ 1/8 & 1/4 & 1/8 \\ 1/16 & 1/8 & 1/16 \end{bmatrix}$$

(2)

Для обеспечения непрерывной обработки информации используется технология двухпортовой памяти. Блоки Register, Register1, Rigister2, Register5-Register10 представляют собой восьмиразрядные регистры данных и объединены в группы по три элемента. Каждая группа является сдвигающим регистром и имеет общую шину входных данных. Тактируются группы по отдельности, обеспечивая заполнение регистров входными данными по n соседних пикселей изображения.

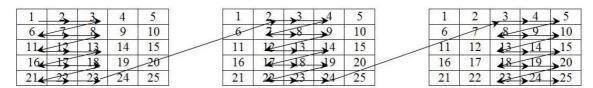

Во входной регистр данных поступают пиксели согласно очередности загрузки, которая определяется алгоритмом обработки. При этом позиция загружаемого пикселя определяется логикой работы блока «Коммутатор адреса 1», которая заключается в том, что заполнение регистра производится по n пикселей (для фильтра размером  $n \times n$ ) из одной строки. После загрузки последнего из n пикселей происходит перемножение с накоплением и одновременным вычислением результата фильтрации, который записывается в определенную область выходной памяти. Следующие n пикселей загружаются из следующей по порядку строки, что обеспечивает равномерное заполнение окна двумерного фильтра из данных сдвиговых регистров и опять производиться вычисление с выгрузкой результата в определенную ячейку памяти. Очередной этап заканчивается переходом с последней строки на первую. Процесс выбора и заполнения сдвигового регистра проиллюстрирован на рисунке 3.

Рисунок 3 – Пример загрузки и обработка пикселей с использованием фильтра размером 3×3

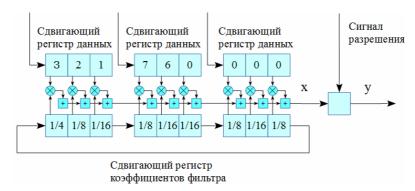

На рисунке 4 представлена структура модуля фильтрации на первом этапе моделирования с загруженными шестью пикселями. Заполнение сдвиговых регистров происходит последовательно, начиная с первого регистра, в каждый сдвигающий регистр заносятся данные из новой строки.

Рисунок 4 – Структура модуля фильтрации на первом этапе моделирования с загружеными шестью пикселями

Следует отметить, что умножение с накоплением происходит при каждой зарузке последующего пикселя, но результат данной операции считается справедливым после загрузки последниго из n пикселей в строке. В этот момент подается сигнал разрешения на запоминание текущего значения свертки данных с коэфициентами фильтра в сдвигающем регистре.

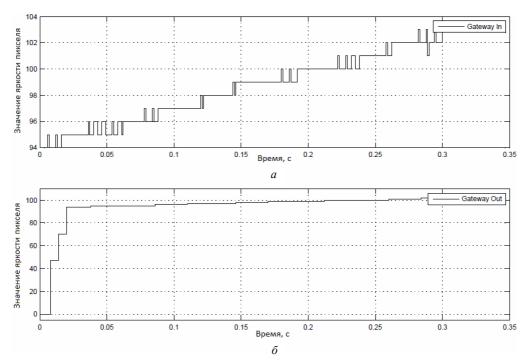

**Результаты и их обсуждение**. На рисунке 5, a продемонстрирована временная диаграмма загрузки изображения на восьмибитную шину данных в Simulink. На рисунке 5,  $\delta$  представлен результат двумерной фильтрации с коэффициентами фильтра, приведенными в выражении (2). Время моделирования рассчитывалось с учетом наглядности графика. При выбранной частоте семплирования 1/1000 и времени моделирования порядка 0.3 секунды обработано порядка 300 пикселей входного изображения.

Рисунок 5 — Временные диаграммы для пикселей: a — исходного изображения;  $\delta$  — выходного изображения

Для оценки скорости обработки изображения использовался специализированный модуль Xilinx Timing Analyzer, который позволяет оценить реальную задержку прохождения сигнала через все логические элементы спроектированной системы и определить максимальную тактовую частоту работы ПЛИС.

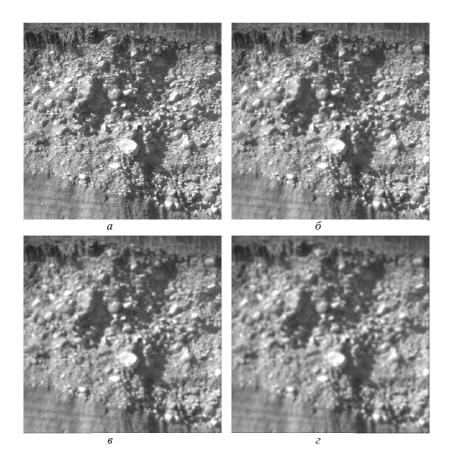

Для определения быстродействия алгоритма фильтрации на базе ПЛИС спроектированы структуры для фильтров с размерами апертур  $3\times3$ ,  $5\times5$ ,  $7\times7$ , определены их основные параметры и максимальная тактовая частота. После проведения тестовых исследований выполнена оптимизация по размещению отдельных логических элементов в структуре ПЛИС и пересчитана тактовая частота работы всей системы. По полученным результатам рассчитано время, требуемое для обработки одного пикселя. В таблице 2 представлены основные характеристики для фильтров различных размеров, на рисунке 6 – результаты фильтрации на ПЛИС с использованием разработанных фильтров.

Таблица 2 – Параметры разработанных фильтров, реализуемых на ПЛИС

| Наименование параметра                                   | Размер апертуры фильтра |       |        |

|----------------------------------------------------------|-------------------------|-------|--------|

| танженование наражегра                                   | 3×3                     | 5×5   | 7×7    |

| Количество секций Slices                                 | 239                     | 619   | 1221   |

| Количество элементов LUTs                                | 172                     | 658   | 1337   |

| Количество триггеров в составе LUT                       | 306                     | 733   | 1411   |

| Количество аппаратных секции DSP48A1                     | 9                       | 25    | 49     |

| Минимальный период частоты тактирования, нс              | 17,11                   | 33,45 | 65,43  |

| Максимальная возможная частота тактирования, МГц         | 58,44                   | 29,89 | 15,28  |

| Максимальная частота тактирования после оптимизации, МГц | 69,8                    | 38,3  | 21,5   |

| Количество тактов для обработки одного пикселя           | 6                       | 10    | 14     |

| Время, требуемое для обработки одного пикселя, нс        | 85,96                   | 261,1 | 651,16 |

Рисунок 6 — Фильтрация изображения с использованием ПЛИС архитектуры FPGA: a — исходное изображения;  $\delta$  — изображение, обработанное фильтром размером  $3\times3$ ; s — изображение, обработанное фильтром размером  $5\times5$ ; s — изображение, обработанное фильтром размером  $7\times7$

Результаты моделирования показывают, что максимальная частота работы двумерных фильтров с размерами апертур 3×3, 5×5, 7×7, реализованных на одном кристалле ПЛИС XC6SLX75 серии Spartran-6, составляет 69.8 МГц, 38,3 МГц, 21.5 МГц соответственно. Для обработки массива данных скользящим окном размерностью 3×3 необходимо не более 6 тактов, размерностью 5×5 – не более 10, а для размерности 7×7 не более 14, т.е. на обработку одного пикселя тратится 85,96 нс, 261,1 нс и 651,16 нс соответственно. Программная реализация процедуры двумерной нерекурсивной фильтрации при использовании персонального компьютера с процессором Intel(R) Core(TM) i5-2450M 2500 МГц с двумя физическими ядрами и четырьмя логическими процессорами в программе MATLAB для окна размером 5×5 занимает 7,4 нс. Таким образом, целесообразность применения ПЛИС для фильтрации изображений очевидна.

Заключение. Использование высокопроизводительных ПЛИС архитектуры FPGA дает возможность повысить быстродействие по сравнению с цифровыми сигнальными процессорами и является перспективным направлением для предварительной обработки крупноформатных изображений. Разработана структура двумерного нерекурсивного фильтра с использованием ПЛИС на основе параллельноконвейерного алгоритма. Представлена модель устройства, которая синтезирована и исследована в программном продукте Simulink. Для аппаратной реализации предлагается использовать ПЛИС XC6SLX75 семейства Spartan-6. В среде разработки Xilinx ISE определена максимальная задержка в цепях внутренней структуры ПЛИС. Проведенные исследования по оценке временных затрат для разработанных структур фильтров подтверждают эффективность их применения.

#### ЛИТЕРАТУРА

1. Реконфигурируемые мультиконвейерные вычислительные структуры / И.А. Каляев [и др.]. – Ростов н/Д: Изд-во ЮНЦ РАН, 2008. – 397 с.

- 2. Зотов, В.Ю. Средства проектирования встраиваемых микропроцессорных систем, реализуемых на основе ПЛИС фирмы Xilinx. М.: Горячая линия-Телеком, 2006. 520 с.

- 3. Тарасов, И.Е. Программируемые логические схемы и их применение в схемотехнических решениях : учеб. пособие / И.Е. Тарасов, Е.Ф. Певцов / Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Московский государственный технический университет радиотехники, электроники и автоматики». М., 2012. 184 с.

- 4. Заливин, А.Н. Использование производительных ПЛИС для обработки изображений / А.Н. Заливин, И.В. Зуев // Научные ведомости Белгородского государственного университета. Сер. История. Политология. Экономика. Информатика. 2014. Вып. № 8-1 (179). Т. 30. С. 90–93.

- 5. Никоноров, А.В. Двумерная рекурсивная фильтрация в GPU системах на основе модели нежесткого следования / А.В. Никоноров, С.Б. Попов, В.А. Фурсов // Научный сервис в сети Интернет: экзафлопсное будущее: тр. Междунар. суперкомпьютерной конф., Новороссийск, 19–24 сент. 2011 г. / Моск. ун-т. Новороссийск, 2011. С. 61–66.

- 6. Байков, Д.А. Использование системы MATLAB+Simulink в проектировании цифровых систем на ПЛИС [Электронный ресурс] / Д.А. Байков // Вычислительные сети. Теория и практика / Network journal. Theory and practice. 2014. Вып. 24. Режим доступа: http://network-journal.mpei.ac.ru/cgi-bin/main.pl?ar=2&l=ru&n=24&pa=8. Дата доступа: 11.05.2015.

Поступила 03.09.2015

### NON-RECURSIVE IMAGE FILTERING USING FPGA

## V. CHERTKOV, R. BOHUSH, A. ANDROSCHUK

We have presented the structure of a two-dimensional non-recursive filter using FPGA for image processing using parallel-pipelined algorithm. The model of the device, which was developed and studied in the software Simulink is provided. For a hardware implementation is proposed to use the FPGA XC6SLX75 Spartan-6 family. Maximum delay in the circuits of the internal structure determined using the Xilinx ISE. The paper includes a calculation processing speed for two-dimensional non-recursive filter of different sizes. Results of experiments are presented.